Semiconductor defect detection gets stronger with AI when the system is used to rank, explain, and route inspection work rather than simply add another classifier on top of an already noisy pipeline. In 2026, the most credible advances are not generic claims that "computer vision finds defects." They are workflows that separate defects of interest from nuisance signals, move the right sites into review, connect those sites to process context, and shorten the loop from inspection to correction.

That matters because advanced-node fabs do not struggle only with finding defects. They struggle with deciding which defects matter, how quickly to review them, and how to connect them back to real process causes across optical tools, e-beam review, wafer maps, equipment traces, and electrical test. At leading nodes, the bottleneck is often signal-to-noise and response time, not raw image availability.

This update reflects the field as of March 20, 2026. It focuses on the parts of the category that feel most real now: automatic defect classification, computer vision, open-set anomaly detection, few-shot learning, virtual metrology, advanced process control, and monitoring loops that make inspection more useful for yield learning rather than just more expensive.

1. Automated Image Analysis and Classification

Automated image analysis is strongest when it triages large inspection volumes into likely defects of interest, likely nuisance, and uncertain cases that deserve fast human review.

The strongest current inspection systems are explicitly built around throughput triage rather than raw image scoring. Siemens reports more than an 80% defect hit rate on wafer verification using engineered features and machine learning, while Onto positions TrueADC around reducing manual review and preserving "unknown" buckets instead of forcing premature labels. Inference: the practical win is not perfect autonomy. It is better queue management for the millions of images and candidate sites a fab already has.

2. Deep Learning-Based Pattern Recognition

Deep pattern recognition matters because wafer defect maps and wafer bin maps still carry a huge amount of root-cause signal when the model can recognize spatial structure more consistently than manual review.

The 2026 Integration review makes clear that wafer map pattern recognition remains central to daily fab operations because spatial patterns such as ring, edge, scratch, or local clusters still point engineers toward likely process stages. The 2024 Electronics paper on polar-coordinate transformed inputs adds a more current signal: model architecture still matters because certain defect classes become easier to separate when positional structure is represented more naturally. Inference: wafer-map AI stays relevant because it compresses large failure surfaces into recognizable process signatures.

3. Feature Extraction for Microscopic Defects

Microscopic defect extraction gets more useful when AI helps isolate buried, low-contrast, or mixed-type micro-defects that optical inspection alone may not characterize well enough.

Applied's SEMVision H20 announcement is useful because it frames the current frontier clearly: faster analysis of buried nanoscale defects through higher-sensitivity e-beam imaging plus AI image recognition. The 2025 dual-modal micro-defect paper points in the same direction from academia, combining optical topography with lightweight classification to deal with mixed-type defects in real time. Inference: high-value inspection increasingly depends on combining better imaging physics with models that can keep up with the resulting detail.

4. Adaptive Thresholding Techniques

Adaptive thresholding matters because at advanced nodes the review burden often comes from nuisance detections, not from a shortage of raw candidates.

Applied's 2023 defect-review perspective is unusually explicit about the nuisance problem, describing false-alarm rates that can exceed 90% in some review flows and the need to separate true defects from noise at scale. KLA's Voyager 1035 messaging describes the same operational problem from the optical-inspection side, using DefectWise to isolate subtle defects of interest from pattern nuisance. Inference: the real thresholding challenge is economic and operational as much as statistical, because every false site burns scarce review time.

5. Automated Root Cause Analysis

Root-cause automation is strongest when AI links defect signatures to process history, tool behavior, and prior incident knowledge instead of leaving engineers to reconstruct each failure path from scratch.

The 2023 Scientific Reports paper on semiconductor failure conclusions shows that machine learning can help rank the textual and structured signals that matter most during failure analysis. Intel's manufacturing RCA case study extends that idea into practice by combining historical knowledge, machine logs, and sensor feeds to shorten incident resolution. Inference: the strongest RCA systems are no longer pure vision systems; they are retrieval and attribution systems built around multiple evidence types.

6. Predictive Maintenance and Tool Health Monitoring

Tool health monitoring is strongest when defect data is treated as an early operational signal for downtime risk and process drift, not only as an after-the-fact quality report.

The 2025 predictive-maintenance study in Computers & Industrial Engineering is helpful here because it uses more than one million real-world semiconductor records and compares several model families rather than implying one algorithm solves everything. The 2025 adaptive-learning comparison adds an important deployment lesson: maintenance models live in non-stationary environments and concept drift matters. Inference: robust tool-health AI depends as much on adaptation and monitoring discipline as on the initial model choice.

7. Real-Time Feedback Loops

Real-time feedback is strongest when inspection and metrology become fast enough to influence the next wafer, next lot, or next recipe move instead of only documenting what already went wrong.

Onto's integrated-metrology messaging and the 2025 optical-metrology review both reinforce the same practical direction: fabs want faster in-line estimates that can feed control, not just delayed measurements that support reports. That is the overlap between inspection, virtual metrology, and APC. Inference: the strongest defect-detection stacks are increasingly evaluated by how well they drive correction speed, not just by how well they classify archived images.

8. Data Fusion from Multiple Sensors

Data fusion matters because optical images, e-beam review, OCD, film metrology, and electrical test each capture different pieces of the same failure story.

Onto's 3D NAND metrology suite is a useful primary-source example because it explicitly describes AI Diffract software combining multiple data streams to meet tighter control requirements. The 2025 optical-metrology review generalizes that same pattern across spectroscopy, inversion, parameter prediction, and defect-detection workflows. Inference: semiconductor AI gets more valuable as it becomes a fusion layer across inspection and metrology rather than another isolated application bolted onto one tool class.

9. Scalable Defect Libraries

Defect libraries are strongest when AI helps fabs build reusable classifiers, preserve uncertain classes, and keep adding new examples without starting over from scratch.

Onto's 2024 deep-learning ADC paper is valuable because it describes the practical structure of an industrial library: multiple model engines, strict escape constraints, and integration with AOI flows. The TrueADC product framing adds an operational detail many academic papers skip: industrial users need "unknown" as a deliberate outcome so the library can expand safely. Inference: modern defect libraries are not static catalogs. They are controlled learning systems with explicit uncertainty management.

10. Unsupervised Anomaly Detection

Unsupervised and open-set methods matter because fabs keep encountering defect patterns that were not present in the original training set and may emerge only under new tools, materials, or layout combinations.

The 2025 open-set wafer-bin-map paper is especially strong because it addresses unknown defect patterns directly in real semiconductor environments and reports over 98% detection performance across multiple new classes. The 2025 IC DefectNCD preprint pushes the same frontier into self-supervised novel class discovery on SEM imagery. Inference: high-value defect AI is moving from closed-world classification toward workflows that can surface new failure modes without pretending every future defect class is already labeled.

11. Domain Adaptation Between Process Nodes

Domain adaptation matters because new nodes and new products rarely begin with large labeled defect sets, yet fabs still need useful models during the earliest learning cycles.

IBM's 2025 ASMC work is a strong current signal here because it shows more than 90% accuracy on SEM defect classification with fewer than 15 images per class using transfer and semi-supervised learning. Siemens' cross-technology-node framework makes the same industrial point from the design-to-fab side, reusing historical process learning to support new-node defect prediction. Inference: transfer learning is no longer a side experiment in semiconductor inspection. It is a necessity for keeping early-node analysis economically viable.

12. Defect Trending and Forecasting

Trending and forecasting are strongest when defect populations are treated as early yield signals that can trigger sampling, review, or containment before a full excursion is obvious.

The 2025 Sensors paper on yield prediction from SEM-detected defects directly connects early defect signals to downstream yield screening, which is exactly where forecasting becomes economically useful. KLA's I-PAT framing adds the reliability side by emphasizing outlier defect populations and part-average testing for automotive requirements. Inference: the best trending systems do not merely plot counts. They turn emerging defect patterns into earlier yield and reliability decisions.

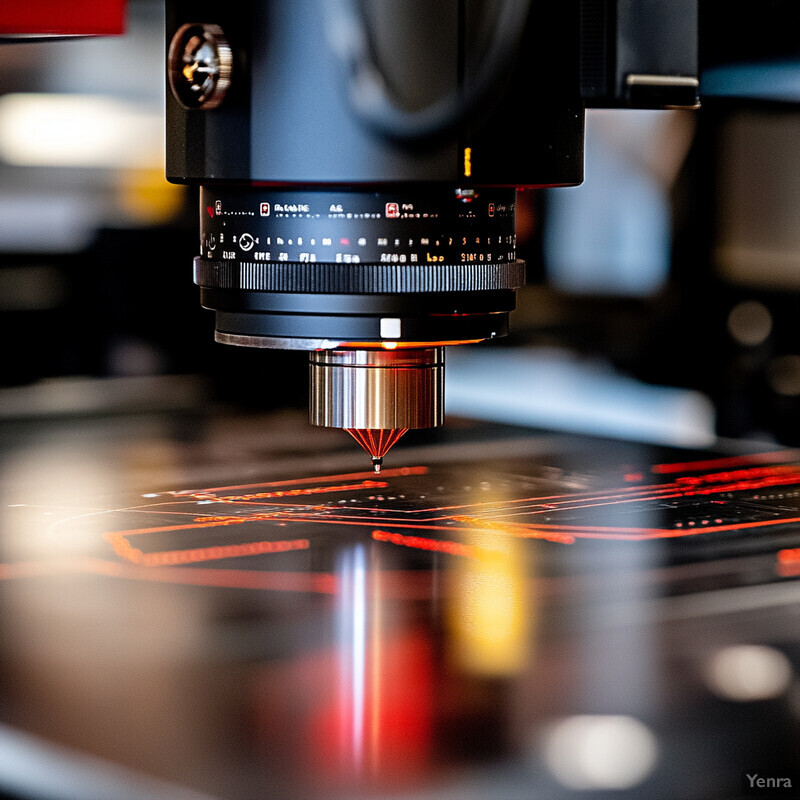

13. Enhanced E-Beam Inspection Efficiency

E-beam efficiency is strongest when AI helps route scarce review capacity toward the sites most likely to contain real yield-relevant defects.

Applied's H20 launch is explicit about the current bottleneck: the industry needs faster review of buried nanoscale defects, not just higher resolution in isolation. KLA's review-portfolio framing makes the same operational point from another angle by emphasizing complete defect paretos and faster excursion detection. Inference: AI makes e-beam useful at scale by improving review prioritization and defect relevance ranking, not only by sharpening imagery.

14. Improved Classification of Gray-Level Defects

Low-contrast defect classification matters because some of the most costly inspection mistakes come from subtle residue, haze, scratches, or pattern deviations that are barely separable from process background.

The 2025 mixed-type micro-defect paper is useful because it targets exactly the class of defects fabs struggle with in production: multiple subtle defect types under real-time constraints. Siemens' 2025 enhancement paper adds a complementary point by using PFA-informed features and reinforcement learning to suppress false positives in defect prediction. Inference: the most useful gains on gray-level defects come from richer contextual modeling and smarter nuisance rejection, not just from turning sensitivity ever higher.

15. Multimodal Data Integration

Multimodal integration is strongest when inspection images, electrical die sorting, and process variables are combined to explain why a defect matters, not just where it sits on a wafer.

The 2024 vBAD work is especially relevant because it shows how rare customer-found failures can be traced back into virtual bad wafers by combining chip-level EDS with large manufacturing data. The 2024 virtual-metrology review generalizes that same logic into fab control: sampled measurement, equipment state, and process variables can be fused to infer quality faster than direct measurement alone. Inference: multimodal AI becomes truly valuable when it helps fabs connect observed defects to electrical impact and process context in one workflow.

16. Reduced Reliance on Human Experts

Human effort is most valuable when it is reserved for edge cases, new classes, and root-cause review instead of being consumed by repetitive image sorting.

Onto's TrueADC product description is one of the clearest current operational sources because it focuses on manual-review reduction, low-confidence handling, and multi-engine decision logic instead of claiming full autonomy. IBM's 2025 ASMC work adds the low-label side by showing that useful classification can be achieved with small image counts when pretrained models are adapted carefully. Inference: the realistic goal in fabs is expert amplification, not expert removal.

17. Continuous Learning and Improvement

Continuous improvement matters because fabs need models that can absorb limited new examples, survive class expansion, and stay useful as layouts, tools, and defect populations evolve.

The 2025 wafer-map incremental-learning paper directly addresses the fab reality of limited novel samples and catastrophic forgetting, while the 2025 lithography dataset-generation paper attacks the adjacent bottleneck of scarce physically grounded training data. Together they show where improvement is headed: class-incremental workflows plus better data generation. Inference: continuous learning in semiconductor inspection is increasingly about controlled library expansion and trustworthy synthetic data, not endless full retraining.

18. Acceleration of Yield Ramp

Yield ramp accelerates when AI helps teams find defect-prone layout regions and likely hotspot classes before enough real product data exists to do that comfortably by hand.

Siemens' 2025 synthetic-layout paper is especially useful because it is explicit about the early-node problem: real product designs are limited, design rules are still settling, and teams still need hotspot signals. The cross-technology-node paper complements that by showing how prior-node learning can shorten the search space for new-layer and new-node defect prediction. Inference: AI speeds yield ramp not by replacing silicon learning, but by choosing better places to look first.

19. Cost Reduction Through Defect Prevention

Cost reduction is strongest when expensive review, packaging rework, and latent-yield loss are avoided by catching defects earlier and on more wafer surfaces.

Onto's EB40 launch is a concrete reminder that valuable defect capture is not confined to frontside inspection; edge and backside defects can migrate into expensive yield loss if they are ignored. Applied's H20 launch points to a parallel cost problem on the review side, where buried nanoscale defects need faster diagnosis to prevent long excursions. Inference: prevention economics improve when fabs extend inspection earlier, deeper, and across more surfaces instead of relying on one late-stage checkpoint.

20. Enhanced Collaboration in the Supply Chain

Collaboration is strongest when design, inspection, yield, and review data can be shared across design houses, fabs, and tool ecosystems without losing defect context.

Siemens' design-to-fab paper makes the integration case clearly by linking hotspot detection, mask-generation accuracy, and fab diagnostics inside one process-improvement arc. Onto's Discover Defect software describes the fab-side version of the same idea, bringing together defect, sort, metrology, WIP, and electrical data in one analysis layer. Inference: the strongest semiconductor AI stacks are becoming collaboration systems for yield knowledge, not just better classifiers inside one inspection box.

Related AI Glossary

- Automatic Defect Classification (ADC) explains the classification layer fabs use to sort defect candidates into actionable classes, nuisance, or unknowns.

- Computer Vision covers the image-understanding backbone behind optical inspection, SEM review, and defect triage.

- Anomaly Detection matters because modern inspection must surface novel and out-of-distribution defect behavior rather than only known classes.

- Virtual Metrology connects defect analytics to faster in-line process estimates and feedback loops.

- Advanced Process Control (APC) explains how inspection and metrology signals can influence recipes before excursions spread.

- Active Learning is useful when fabs want to spend scarce engineering labels on the most informative uncertain defect cases.

- Model Monitoring helps frame drift, performance decay, and retraining discipline in long-running fab AI systems.

Sources and 2026 References

- Siemens: Machine Learning Based Wafer Defect Detection.

- Onto Innovation: TrueADC Software.

- Integration (2026): Review: Application and Development of Machine Learning in Semiconductor Manufacturing for Automated Wafer Map Pattern Recognition and Classification.

- Electronics (2024): Development of a Wafer Defect Pattern Classifier Using Polar Coordinate System Transformed Inputs and Convolutional Neural Networks.

- Applied Materials (2025): Applied Materials Accelerates Chip Defect Review with Next-Gen eBeam System.

- Engineering Applications of Artificial Intelligence (2025): Mixed-Type Micro-Defect Detection in Semiconductor Wafers.

- Applied Materials (2023): Separating the Signal from the Noise: Combining Advanced Imaging with AI for Chip Defect Review.

- KLA (2023): Voyager 1035 Defect Inspection System.

- Scientific Reports (2023): Root Cause Prediction for Failures in Semiconductor Industry, a Genetic Algorithm-Machine Learning Approach.

- Intel / Articul8: Manufacturing Root Cause Analysis.

- Computers & Industrial Engineering (2025): Predictive Maintenance in Semiconductor Manufacturing.

- IFAC-PapersOnLine (2025): Adaptive Learning Mode Comparison for Predictive Maintenance Systems.

- Onto Innovation (2021): Customer Selection of Comprehensive Integrated Metrology Suite.

- Micromachines (2025): AI-Powered Next-Generation Technology for Semiconductor Optical Metrology: A Review.

- Onto Innovation / SPIE (2024): Using Deep Learning ADC for Defect Classification for Automatic Defect Inspection.

- Computers in Industry (2025): Enhanced Detection of Unknown Defect Patterns on Wafer Bin Maps Based on an Open-Set Recognition Approach.

- arXiv (2025): Image-Intrinsic Priors for Integrated Circuit Defect Detection and Novel Class Discovery via Self-Supervised Learning.

- ASMC / arXiv (2025): Semiconductor SEM Image Defect Classification Using Supervised and Semi-Supervised Learning with Vision Transformers.

- Siemens (2024): An AI/ML Approach with Cross-Technology Node Learning for Multi-Layer Process Defect Predictions.

- Sensors (2025): Detecting Important Features and Predicting Yield from Defects Detected by SEM in Semiconductor Production.

- KLA: Inline Defect Part Average Testing (I-PAT).

- Electronics (2024): Chip-Level Defect Analysis with Virtual Bad Wafers Based on Huge Big Data Handling for Semiconductor Production.

- Expert Systems with Applications (2024): Virtual Metrology in Semiconductor Manufacturing: Current Status and Future Prospects.

- Computers in Industry (2025): Incremental Learning Strategies for Improved Detection of Unknown Defects in Wafer Maps with Limited Samples.

- arXiv (2025): A Physics-Constrained, Design-Driven Methodology for Defect Dataset Generation in Optical Lithography.

- Siemens (2025): Guided Random Synthetic Layout Generation and Machine Learning-Based Defect Prediction.

- Onto Innovation (2022): New EB40 All-Surface Inspection Module for Wafer Fabs and Advanced Packaging.

- Siemens: Reduction of Systematic Defects with Machine Learning from Design to Fab.

- Onto Innovation: Discover Defect Software.

Related Yenra Articles

- Micro-Fabrication Process Control goes deeper on run-to-run control, virtual metrology, and the process tuning side of yield improvement.

- Digital Twin Modeling in Manufacturing extends the topic into simulation-backed manufacturing monitoring and what-if analysis.

- Materials Science Research connects semiconductor inspection to broader microscopy, characterization, and low-data scientific AI workflows.

- Industrial Robotics broadens the discussion to machine vision, factory automation, and physical execution on manufacturing lines.