On November 28, 2017, Toshiba Memory Corporation started sampling Universal Flash Storage (UFS) devices utilizing Toshiba Memory Corporation's 64-layer 3D flash memory known as BiCS FLASH. Universal Flash Storage (UFS) is a product category for a class of embedded memory products built to the JEDEC UFS standard specification. The new UFS devices meet performance demands for applications that require high-speed read/write performance and low power consumption, including mobile devices such as smartphones and tablets, and augmented and virtual reality systems.

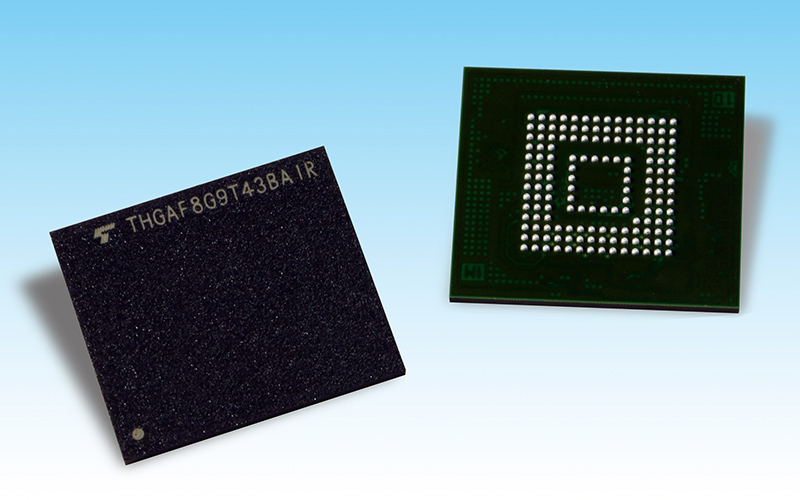

The new 64-layer 3D flash memory line-up will be available in four capacities: 32GB, 64GB, 128GB and 256GB. All of the devices integrate flash memory and a controller in a single, JEDEC-standard 11.5 x 13mm package. The controller performs error correction, wear leveling, logical-to-physical address translation and bad-block management, allowing users to simplify system development.

All four devices are compliant with JEDEC UFS Ver2.1, including HS-GEAR3, which has a theoretical interface speed of up to 5.8Gbps per lane (x2 lanes = 11.6Gbps) while also suppressing any increase in power consumption. Sequential read and write performance of the 64GB device are 900MB/s and 180MB/s, while the random read and write performance are around 200% and 185% better, respectively, than those of previous generation devices. Due to its serial interface, UFS supports full duplexing, which enables both concurrent reading and writing between the host processor and UFS device.

What is Universal Flash Storage?

Universal Flash Storage (UFS) is a common flash storage specification for digital cameras, mobile phones and consumer electronic devices. It aims to bring higher data transfer speed and increased reliability to flash memory storage, while reducing market confusion and removing the need for different adapters for different types of card.

What is 3D Flash Memory?

3D flash memory stacks memory cells vertically and uses a charge trap flash architecture. The vertical layers allow larger areal bit densities without requiring smaller individual cells.